**LS7166**

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (516) 271-0400 FAX (516) 271-0405

# 24 BIT MULTIMODE COUNTER

October 1997

#### **FEATURES:**

- Programmable modes are: Up/Down, Binary, BCD, 24 Hour Clock, Divide-by-N, X1 or X2 or X4 Quadrature and Single Cycle.

- DC to 20 MHZ Count Frequency.

- 8-Bit I/O Bus for Microprocessor Communication and Control.

- 24-Bit comparator for pre-set count comparison.

- Readable status register.

- Input/Output TTL and CMOS compatible.

- 5 Volt operation.

- 20 pin Plastic DIP

### **GENERAL DESCRIPTION:**

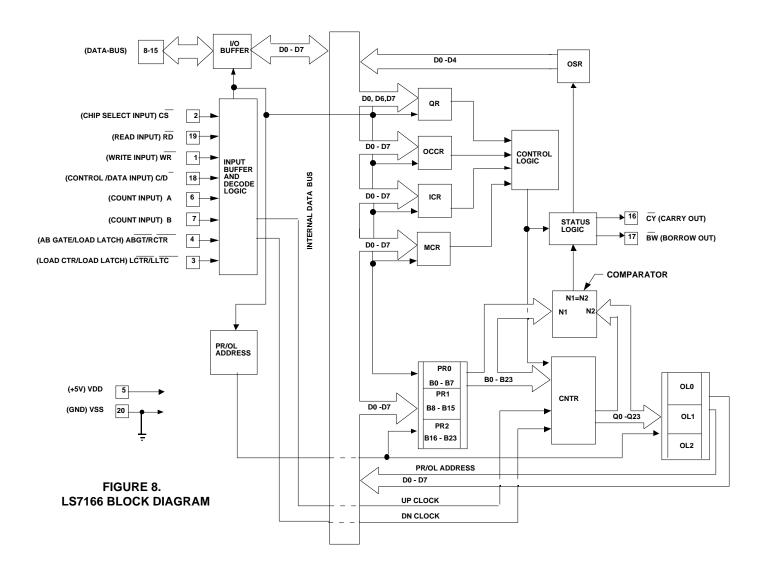

The LS7166 is a monolithic, CMOS Silicon Gate, 24-bit counter that can be programmed to operate in several different modes. The operating mode is set up by writing control words into internal control registers (see Figure 8). There are three 6-bit and one 2-bit control registers for setting up the circuit functional characteristics. In addition to the control registers, there is a 5-bit output status register (OSR) that indicates the current counter status. The LS7166 communicates with external circuits through an 8-bit three state I/O bus. Control and data words are written into the LS7166 through the bus. In addition to the I/O bus, there are a number of discrete inputs and outputs to facilitate instantaneous hardware based control functions and instantaneous status indication.

## **REGISTER DESCRIPTION:**

Internal hardware registers are accessible through the I/O bus (D0 - D7) for READ or WRITE when CS = 0. The  $C/\overline{D}$  input selects between the control registers (C/D = 1) and the data registers (C/D = 0) during a READ or WRITE operation. (See Table 1)

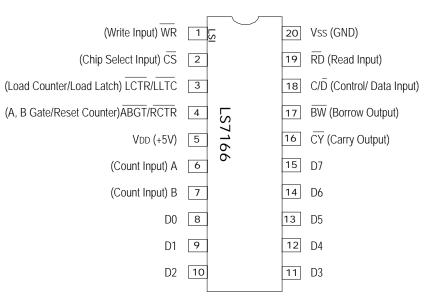

## **PIN ASSIGNMENT - TOP VIEW** STANDARD 20 PIN PLASTIC DIP

FIGURE 1

The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, nor for any infringements of patent rights of others which may result from its use.

**TABLE 1 - Register Addressing Modes**

| <b>D7</b><br>X |        | C/D X  |      |         |        | COMMENT Disable Chip for READ/WRITE                                                                     |

|----------------|--------|--------|------|---------|--------|---------------------------------------------------------------------------------------------------------|

| 0              |        | 1      |      |         | -      | Write to Master Control Register (MCR)                                                                  |

| 0              | 1      | 1      | 1    | J       | 0      | Write to input control register (ICR)                                                                   |

| 1              | 0      | 1      | 1    | _C      | 0      | Write to output/counter control register (OCCR)                                                         |

| 1<br>X         | 1<br>X | 1<br>0 | 1    | L<br>JL | 0<br>0 | Write to quadrature register (QR) Write to preset register (PR) and increment register address counter. |

| X              | Χ      | 0      | Ţ    | 1       | 0      | Read output latch (OL) and increment register address counter                                           |

| X              | Χ      | 1      |      | 1       | 0      | Read output status register (OSR).                                                                      |

| Χ              | = D    | on't ( | Care |         |        |                                                                                                         |

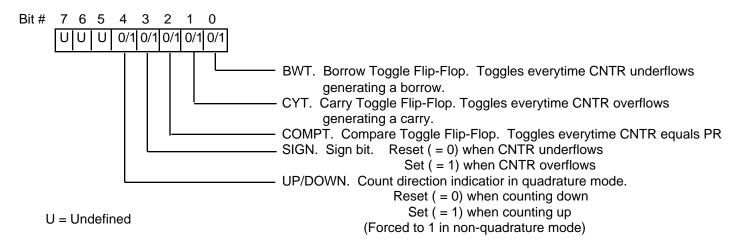

**OSR (Output Status Register).** Indicates CNTR status: Accessed by: READ when  $C/\overline{D} = 1$ ,  $\overline{CS} = 0$ .

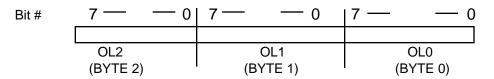

**OL(Output latch)**. The OL is the output port for the CNTR. The 24 bit CNTR Value at any instant can be accessed by performing a CNTR to OL transfer and then reading the OL in 3 READ cycle sequence of Byte 0 (OL0), Byte 1 (OL1) and Byte 2 (OL2). The address pointer for OL0/OL1/OL2 is automatically incremented with each READ cycle. Accessed by: READ when  $C/\overline{D} = 0$ ,  $\overline{CS} = 0$ .

Standard Sequence for Loading and Reading OL:

3 -> MCR ; Reset OL address pointer and Transfer CNTR to OL

READ OL ; Read Byte 0 and increment address READ OL ; Read Byte 1 and increment address READ OL ; Read Byte 2 and increment address

PR (Preset register). The PR is the input port for the CNTR. The CNTR is loaded with a 24 bit data via the PR. The data is first written into the PR in 3 WRITE cycle sequence of Byte 0 (PR0), Byte 1 (PR1) and Byte 2 (PR2). The address pointer for PR0/PR1/PR2 is automatically incremented with each write cycle. Accessed by: WRITE when  $C/\overline{D} = 0$ ,  $\overline{CS} = 0$ .

7-----0 7-----0 7-----0

PR2 PR1 PR0 Bit # (BYTE 2)

Standard Sequence for Loading PR and Reading CNTR:

1 → MCR ; Reset PR address pointer

; Load Byte 0 and into PR0 increment address WRITE PR WRITE PR ; Load Byte 0 and into F

WRITE PR ; Load Byte 1 and into F

WRITE PR ; Load Byte 2 and into F

8 → MCR ; Transfer PR to CNTR ; Load Byte 1 and into PR1 increment address ; Load Byte 2 and into PR3 increment address

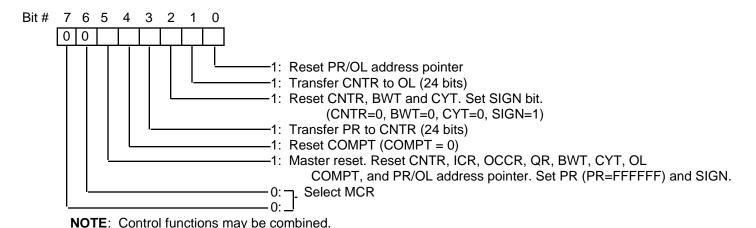

MCR (Master Control Register). Performs register reset and load operations. Writing a "non-zero" word to MCR does not require a follow-up write of an "all-zero" word to terminate a designated operation. Accessed by: WRITE when  $C/\overline{D} = 1$ ,  $\overline{CS} = 0$ .

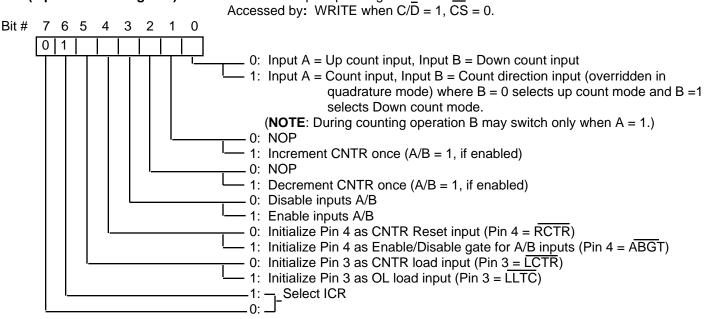

ICR (Input Control Register). Initializes counter input operating modes.

**NOTE**: Control functions may be combined.

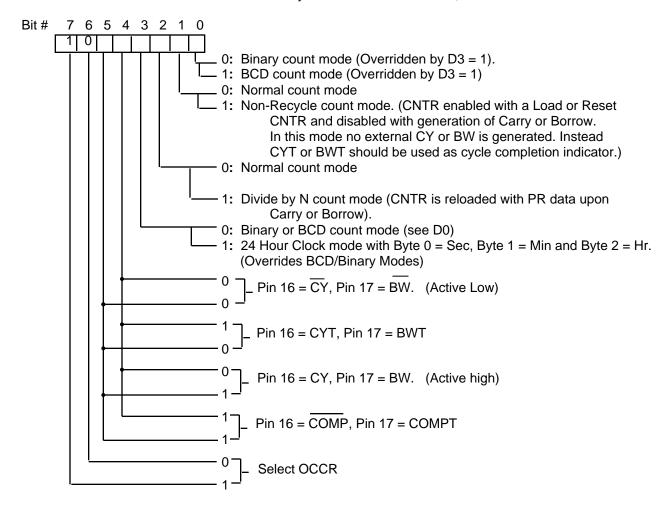

# OCCR (Output Control Register) Initializes CNTR and output operating modes. Accessed by : WRITE when $C/\overline{D} = 1$ , $\overline{CS} = 0$ .

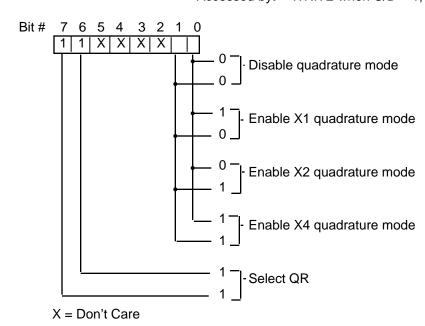

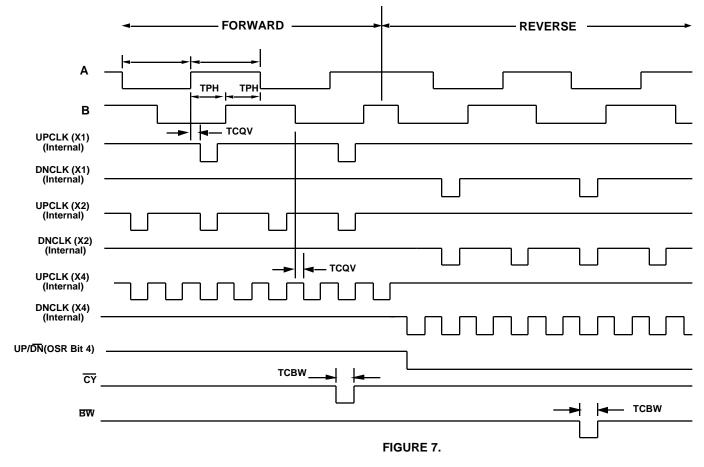

# **QR (Quadrature Register).** Selects quadrature count mode (See Fig. 7) Accessed by: WRITE when $C/\overline{D} = 1$ , $\overline{CS} = 0$ .

\_..\_ ..... .

#### I/O DESCRIPTION:

### (See REGISTER DESCRIPTION for I/O Prgramming.)

**Data-Bus (D0-D7) (Pin 8-Pin 15).** The 8-line data bus is a three-state I/O bus for interfacing with the system bus.

CS (Chip Select Input) (Pin 2). A logical "0" at this input enables the chip for Read and Write.

RD (Read Input) (Pin 19). A logical "0" at this input enables the OSR and the OL to be read on the data bus.

**WR (Write Input) (Pin 1)** A logical "0" at this input enables the data bus to be written into the control and data registers.

**C/D (Control/Data Input) (Pin 18).** A logical "1" at this input enables a control word to be written into one of the four control registers or the OSR to be read on the I/O bus. A logical "0" enables a data word to be written into the PR, or the OL to be read on the I/O bus.

**A (Pin 6).** Input A is a programmable count input capable of functioning in three different modes, such as up count input, down count input and quadrature input.

**B** (Pin 7). Input B is also a programmable count input that can be programmed to function either as down count input, or count direction control gate for input A, or quadrature input. When B is programmed as count direction control gate, B=0 enables A as the Up Count input and B=1 enables A as the Down Count input.

**ABGT/RCTR** (PIN 4). This input can be programmed to function as either inputs A and B enable gate or as external counter reset input. A logical "0" is the active level on this input.

LCTR/LLTC (PIN 3). This input can be programmed to function as the external load command input for either the CNTR or the OL. When programmed as counter load input, the counter is loaded with the data contained in the PR. When programmed as the OL load input, the OL is loaded with data contained in the CNTR. A logical "0" is the active level on this input.

CY (Pin 16). This output can be programmed to serve as one of the following:

- A. CY. Complemented Carry out (active "0").

- B. CY. True Carry out (active "1").

- C. CYT. Carry Toggle flip-flop out.

- D. COMP. Comparator out (active "0")

**BW** (Pin 17). This output can be programmed to serve as one of the following:

- A. BW. Complemented Borrow out (active "0").

- B. BW. True Borrow out (active "1").

- C. BWT. Borrow Toggle flip-flop out.

- D. COMPT. Comparator Toggle output.

VDD (Pin 5). Supply voltage positive terminal.

Vss (Pin 20). Supply voltage negative terminal.

## **Absolute Maximum Ratings:**

| Parameter             | Symbol  | Values         | Unit  |

|-----------------------|---------|----------------|-------|

| Voltage at any input  | VIN     | Vss5 to VDD+.5 | Volts |

| Operating Temperature | TA      | 0 to +70       | oC    |

| Storage Temperature   | Tstg    | -65 to +150    | oC    |

| Supply Voltage        | VDD-VSS | +7.0           | Volts |

#### **DC Electrical Characteristics**. (All voltages referenced to Vss.

$TA = 0^{\circ}$  to  $70^{\circ}C$ , VDD = 4.5V to 5.5V, fc = 0, unless otherwise specified)

| Parameter                              | Symbol | Min. Value | Max.Value | Unit  | Remarks            |

|----------------------------------------|--------|------------|-----------|-------|--------------------|

| Supply Voltage                         | VDD    | 4.5        | 5.5       | Volts | -                  |

| Supply Current                         | IDD    | -          | 350       | μΑ    | Outputs open       |

| Input Low Voltage                      | VIL    | 0          | 0.8       | Volts | -                  |

| Input High Voltage                     | VIH    | 2.0        | VDD       | Volts | -                  |

| Output Low Voltage                     | VOL    | -          | 0.4       | Volts | 4mA Sink           |

| Output High Voltage                    | VOH    | 2.5        | -         | Volts | 200µA Source       |

| Input Current                          | -      | -          | 15        | nA    | Leakage<br>Current |

| Output Source Current                  | ISRC   | 200        | -         | μA    | VOH = 2.5V         |

| Output Sink Current Data Bus Off-State | ISINK  | 4          | -         | mA    | VOL = 0.4V         |

| Leakage Current                        | -      | -          | 15        | nA    | -                  |

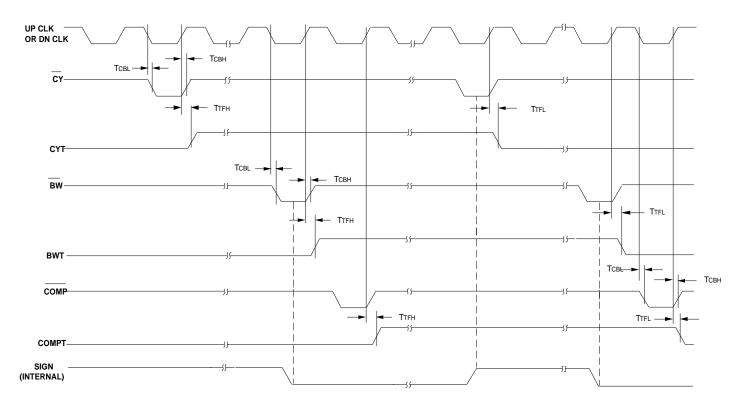

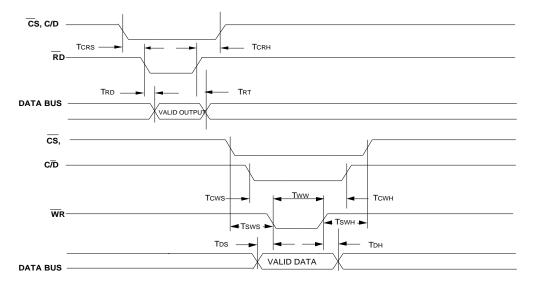

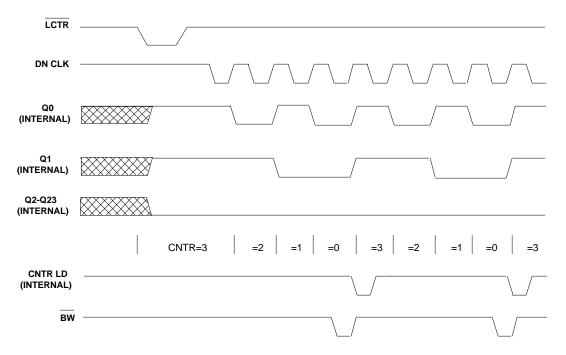

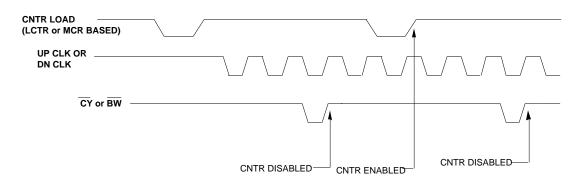

**TRANSIENT CHARACTERISTICS** (See Timing Diagrams in Fig. 2 thru Fig. 7, VDD=4.5V to 5.5V,  $TA=0^{\circ}$  to  $70^{\circ}C$ , unless otherwise specified)

| Parameter Clock A/B "Low" Clock A/B "High"                     | Symbol<br>TCL<br>TCH | <b>Min.Value</b><br>20<br>30 | Max.Value<br>No Limit<br>No Limit | Unit<br>ns<br>ns |

|----------------------------------------------------------------|----------------------|------------------------------|-----------------------------------|------------------|

| Clock A/B Frequency<br>(See NOTE 1)<br>Clock UP/DN Reversal    | fc<br>Tupp           | 0<br>100                     | 20                                | MHz<br>ns        |

| Delay LCTR Positive edge to                                    | TLC                  | 100                          | _                                 | ns               |

| the next A/B positive or negative edge delay                   | 120                  | 100                          |                                   | 110              |

| Clock A/B to<br>CY/BW/COMP "low"<br>propagation delay          | TCBL                 | -                            | 65                                | ns               |

| Clock A/B to CY/BW/COMP "high" propagation delay               | Тсвн                 | -                            | 85                                | ns               |

| LCTR and LLTC pulse width                                      | TLCW                 | 60                           | -                                 | ns               |

| Clock A/B to CYT, BWT<br>and COMPT "high"<br>propagation delay | Ттғн                 | -                            | 100                               | ns               |

| Clock A/B to CYT, BWT<br>and COMPT "low"<br>progagation delay  | TTFL                 | -                            | 100                               | ns               |

| WR pulse width                                                 | Tww                  | 60                           | -                                 | ns               |

| RD to data out delay (CL=20pF)                                 | TR                   | -                            | 110                               | ns               |

| CS, RD Terminate to<br>Data-Bus Tri-State                      | TRT                  | -                            | 30                                | ns               |

| Data-Bu <u>s s</u> et-up time for WR                           | TDS                  | 15                           | -                                 | ns               |

| Data-Bus hold time for $\overline{WR}$                         | TDH                  | 30                           | -                                 | ns               |

| C/D,CS set-up time for RD                                      | TCRS                 | 0                            | -                                 | ns               |

| C/D, CS hold time for RD                                       | TCRH                 | 0                            | -                                 | ns               |

| C/D set-up time for WR                                         | Tows                 | 15                           | -                                 | ns               |

| C/D hold time for WR                                           | TCWH                 | 30<br>15                     | -                                 | ns               |

| CS set-up time for WR<br>CS holdtime for WR                    | Tsws<br>Tswh         | 0                            | -                                 | ns<br>ns         |

| Quadrature Mode:<br>Clock A/B Validation delay<br>(See NOTE 2) | Tcqv                 | -                            | 160                               | ns               |

| A and B phase delay                                            | Трн                  | 208                          | -                                 | ns               |

| Clock A/B frequency                                            | fcQ                  | -                            | 1.2                               | MHz              |

| CY,BW,COMP pulse width                                         | TCBW                 | 75                           | 180                               | ns               |

NOTE 1: A) In Divide by N mode, the maximum clock frequency is 10 MHZ.

B) The maximum frequency for valid CY, BW, CYT, BWT, COMP, COMPT is 10 MHz.

NOTE 2: In quadrature mode A/B inputs are filtered and required to be stable for at least Tcqv length to be valid.

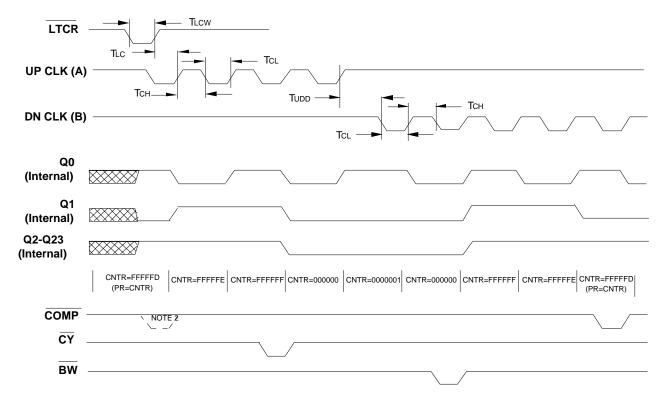

FIGURE 2. LOAD COUNTER, UP CLOCK, DOWN CLOCK, COMPARE OUT, CARRY, BORROW

**NOTE 1**: The counter in this example is assumed to be operating in the binary mode.

**NOTE 2**: No COMP output is generated here, although PR=CNTR. COMP output is disabled with a counter load command and enabled with the rising edge of the next clock, thus eliminating invalid COMP outputs whenever the CNTR is loaded from the PR.

NOTE 3: When UP Clock is active, the DN Clock should be held "HIGH" and vice versa.

FIGURE 3. CLOCK TO CY/BW OUTPUT PROPAGATION DELAYS

FIGURE 4. READ/WRITE CYCLES

NOTE: EXAMPLE OF DIVIDE BY 4 IN DOWN COUNT MODE FIGURE 5. DIVIDE BY N MODE

FIGURE 6. CYCLE ONCE MODE

**QUADRATURE MODE INTERNAL CLOCKS**

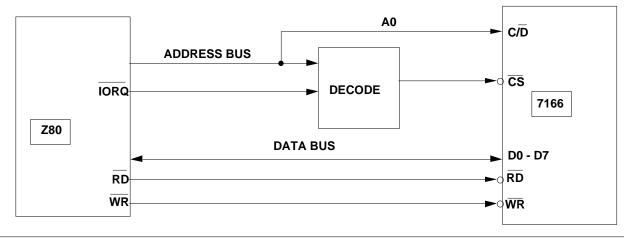

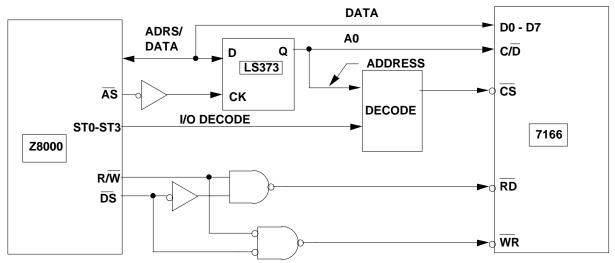

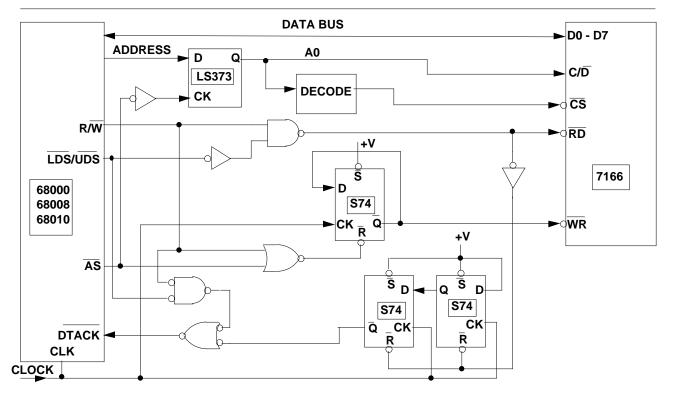

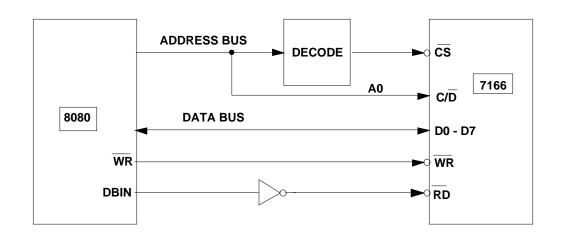

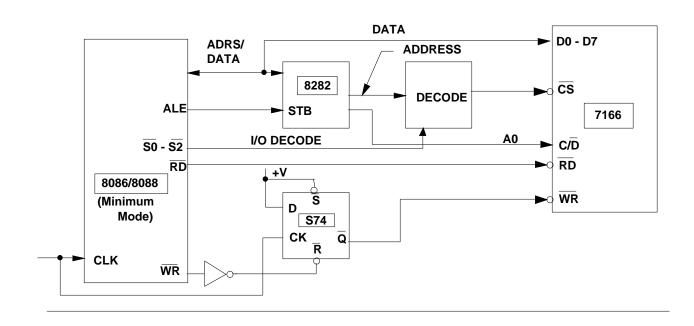

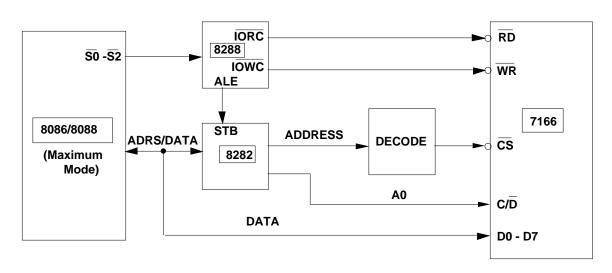

# **LS7166 INTERFACE EXAMPLES**

# **LS7166 INTERFACE EXAMPLES**